Microblaze Compatible Verilog Core

Today, I released the new design to my aeMB core, which is a Xlinx Microblaze compatible processor core, implemented in Verilog. This is a complete rewrite of my previous aeMB core. I had not updated that core for several years and I thought that it was about time to give it an update.

The Microblaze is a 32-bit RISC microprocessor core that is capable of running Linux. It has a complete GCC toolchain and standard libraries. This made it attractive as the software tools were already in place. Since it used GCC, there was plenty of software code lying around as well. What made it more attractive was the fact that I had been given unofficial permission to work on the design.

The reason for the complete rewrite is because the previous one suffered from two fatal flaws. First, the design was not made to handle interrupts nor exceptions. This severely limited the use of the core to pure data processing and not input/output work. Second, the design was a four-stage pipeline, and not a three-stage one. This made it architecturally incompatible with the Microblaze.

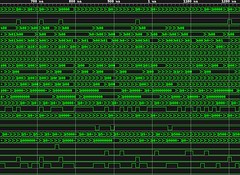

The image shows a screenshot of the core timing diagram, under simulation, running some C code compiled with GCC. Recently, I had to update my ae18 core as it had some trouble synthesising. So, I ran the aeMB core through synthesis, just to check that the design is implementable. I'm tempted to put it through the whole ASIC design flow just for the heck of it, since I have the tools to do it now.

I had recently come across a book, in the library, that tried to show how to design a simple microprocessor using Verilog. I had been asked to conduct a class before, by one of my clients, but I never thought much about it until now. In my opinion, it wasn't a very good book. This started me thinking that maybe I should write a book on microprocessor design.

There are plenty of books that talk about microprocessor architecture from an abstract perspective, without the necessary implementation details. Hence, there is a disconnect between idea and implementation, which not many people bridge. Who knows, this might actually be a good idea to pursue. I should mull over it a bit more.

The Microblaze is a 32-bit RISC microprocessor core that is capable of running Linux. It has a complete GCC toolchain and standard libraries. This made it attractive as the software tools were already in place. Since it used GCC, there was plenty of software code lying around as well. What made it more attractive was the fact that I had been given unofficial permission to work on the design.

The reason for the complete rewrite is because the previous one suffered from two fatal flaws. First, the design was not made to handle interrupts nor exceptions. This severely limited the use of the core to pure data processing and not input/output work. Second, the design was a four-stage pipeline, and not a three-stage one. This made it architecturally incompatible with the Microblaze.

The image shows a screenshot of the core timing diagram, under simulation, running some C code compiled with GCC. Recently, I had to update my ae18 core as it had some trouble synthesising. So, I ran the aeMB core through synthesis, just to check that the design is implementable. I'm tempted to put it through the whole ASIC design flow just for the heck of it, since I have the tools to do it now.

I had recently come across a book, in the library, that tried to show how to design a simple microprocessor using Verilog. I had been asked to conduct a class before, by one of my clients, but I never thought much about it until now. In my opinion, it wasn't a very good book. This started me thinking that maybe I should write a book on microprocessor design.

There are plenty of books that talk about microprocessor architecture from an abstract perspective, without the necessary implementation details. Hence, there is a disconnect between idea and implementation, which not many people bridge. Who knows, this might actually be a good idea to pursue. I should mull over it a bit more.

No comments:

Post a Comment